Product Summary

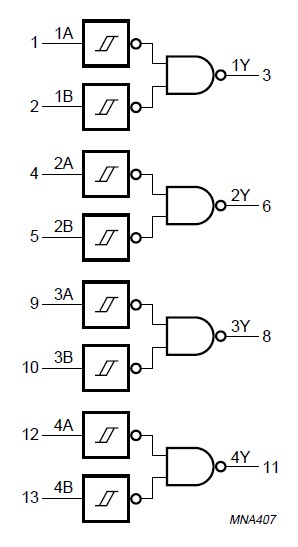

The 74AHC132D is a Quad 2-input NAND Schmitt trigger. It is specified in compliance with JEDEC standard No. 7A. The device contains four 2-input NAND gates which accept standard input signals. The 74AHC132D is capable of transforming slowly changing input signals into sharply defined, jitter free output signals. The gate switches at different points for positive and negative-going signals. The difference between the positive voltage VT+ and the negative VT- is defined as the hysteresis voltage VH.

Parametrics

74AHC132D absolute maximum ratings: (1)VCC DC voltage: -0.5 to +7.0 V; (2)VI input voltage range: -0.5 to +7.0 V; (3)IIK DC input diode curren: -20 mA; (4)IOK DC output diode current: ±20 mA; (5)IO DC output source or sink current: ±25 mA; (6)ICC DC VCC or GND current: ±75 mA; (7)Tstg storage temperature range: -65 to +150 ℃; (8)PD power dissipation per package: 500 mW.

Features

74AHC132D features: (1)ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V; MM EIA/JESD22-A115-A exceeds 200 V CDM EIA/JESD22-C101 exceeds 1000 V; (2)Balanced propagation delays; (3)Inputs accepts voltages higher than VCC; (4)For AHC only: operates with CMOS input levels; (5)For AHCT only: operates with TTL input levels; (6)Specified from -40 to +85 and +125 ℃.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74AHC132D |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74AHC132D,112 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

|

74AHC132D,118 |

NXP Semiconductors |

Gates (AND / NAND / OR / NOR) QUAD 2-INPUT NAND |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))